## **Freescale Semiconductor**

#### **Technical Data**

MC144110/D Rev. 2, 1/2005

## MC144110

Package Information

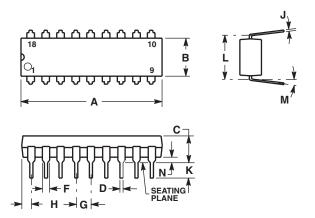

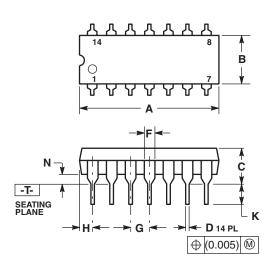

P Suffix

Plastic DIP

Case 707

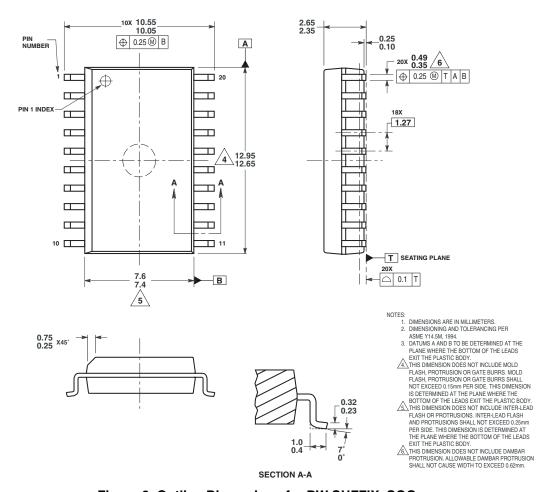

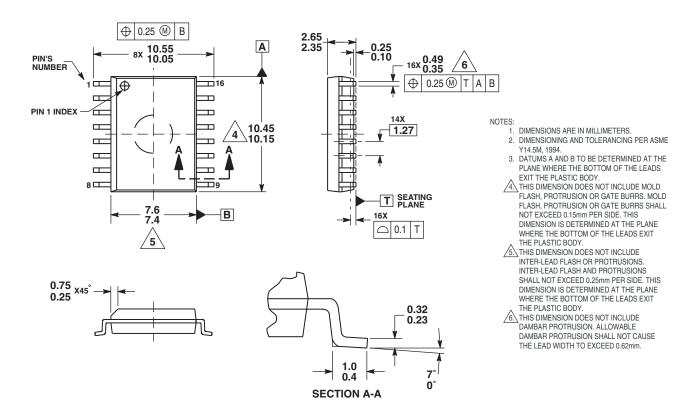

Package Information DW Suffix SOG Package Case 751D

## MC144111

Package Information

P Suffix

Plastic DIP

Case 646

Package Information DW Suffix SOG Package Case 751G

### Ordering Information

| Device     | Package     |

|------------|-------------|

| MC144110P  | Plastic DIP |

| MC144110DW | SOG         |

| MC144111P  | Plastic DIP |

| MC144111DW | SOG         |

#### **Contents**

| 1 | Introduction 1              |

|---|-----------------------------|

| 2 | Electrical Specifications 4 |

| 3 | Switching Characteristics 5 |

| 4 | Pin Descriptions 8          |

| 5 | Packaging                   |

# MC144110 and MC144111

Digital-to-Analog Converters with Serial Interface CMOS LSI

## 1 Introduction

The MC144110 and MC144111 are low-cost 6-bit D/A converters with serial interface ports to provide communication with CMOS microprocessors and microcomputers. The MC144110 contains six static D/A converters; the MC144111 contains four converters.

Due to a unique feature of these DACs, the user is permitted easy scaling of the analog outputs of a system. Over a 5 to 15 V supply range, these DACs may be directly interfaced to CMOS MPUs operating at 5 V.

- Direct R-2R Network Outputs

- Buffered Emitter-Follower Outputs

- Serial Data Input

- Digital Data Output Facilitates Cascading

- Direct Interface to CMOS μP

- Wide Operating Voltage Range: 4.5 to 15 V

- Wide Operating Temperature Range: 0 to 85°C

- Software Information is Contained in Document M68HC11RM/AD

Freescale reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

© Freescale Semiconductor, Inc., 2005. All rights reserved.

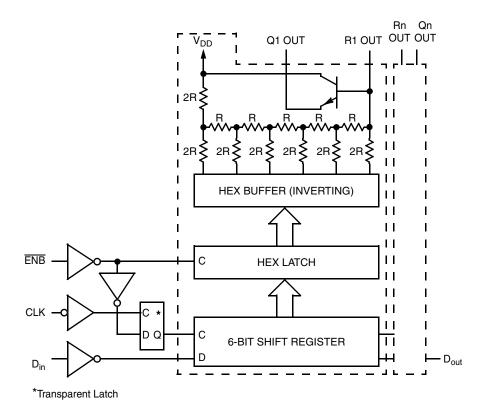

Figure 1. Block Diagram

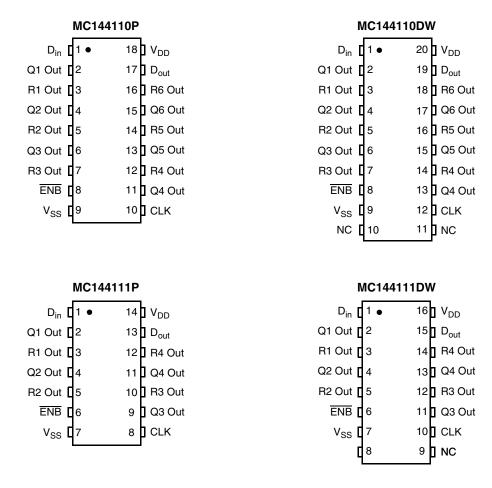

NC = No Connection

Figure 2. Pin Assignments

## 2 Electrical Specifications

Table 1. Maximum Ratings (Voltages referenced to V<sub>SS</sub>)

|                                                         | Ratings                                                         | Symbol           | Value                          | Unit |

|---------------------------------------------------------|-----------------------------------------------------------------|------------------|--------------------------------|------|

| DC Supply Volt                                          | age                                                             | V <sub>DD</sub>  | - 0.5 to + 18                  | V    |

| Input Voltage, A                                        | All Inputs                                                      | V <sub>in</sub>  | - 0.5 to V <sub>DD</sub> + 0.5 | V    |

| DC Input Curre                                          | nt, per Pin                                                     | I                | ± 10                           | mA   |

| Power Dissipati $T_A = 70^{\circ}C$ $T_A = 85^{\circ}C$ | on (Per Output)<br>MC144110<br>MC144111<br>MC144110<br>MC144111 | Рон              | 30<br>50<br>10<br>20           | mW   |

| Power Dissipation (Per Package)  T <sub>A</sub> = 70°C  |                                                                 | P <sub>D</sub>   | 100<br>150<br>25<br>50         | mW   |

| Storage Temperature Range                               |                                                                 | T <sub>stg</sub> | - 65 to + 150                  | °C   |

This device contains protection circuitry to guard against damage due to high static voltages or electric fields; however, it is advised that precautions be taken to avoid application of voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation it is recommended that  $V_{in}$  and  $V_{out}$  be constrained to the range  $V_{SS} \leq (V_{in} \text{ or } V_{out}) \leq V_{DD}$ .

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either  $V_{SS}$  or  $V_{DD}$ ).

Table 2. Electrical Characteristics (Voltages referenced to  $V_{SS}$ ,  $T_A = 0$  to  $85^{\circ}C$  unless otherwise indicated)

| Symbol            | Parameter                                             | Test Conditions                            | V <sub>DD</sub> | Min             | Max               | Unit |

|-------------------|-------------------------------------------------------|--------------------------------------------|-----------------|-----------------|-------------------|------|

| V <sub>IH</sub>   | High-Level Input Voltage (D <sub>in</sub> , ENB, CLK) |                                            | 5<br>10<br>15   | 3.0<br>3.5<br>4 | -<br>-<br>-       | V    |

| V <sub>IL</sub>   | Low-Level Input Voltage (D <sub>in</sub> , ENB, CLK)  |                                            | 5<br>10<br>15   | -<br>-<br>-     | 0.8<br>0.8<br>0.8 | V    |

| I <sub>OH</sub>   | High-Level Output Current (Dout)                      | V <sub>out</sub> = V <sub>DD</sub> - 0.5 V | 5               | - 200           | -                 | μА   |

| I <sub>OL</sub>   | Low-Level Output Current (Dout)                       | V <sub>out</sub> = 0.5 V                   | 5               | 200             | -                 | μА   |

| I <sub>DD</sub>   | Quiescent Supply Current MC144110 MC144111            | I <sub>out</sub> = 0 μA                    | 15<br>15        | -               | 12<br>8           | mA   |

| I <sub>in</sub>   | Input Leakage Current (Din, ENB, CLK)                 | V <sub>in</sub> = V <sub>DD</sub> or 0 V   | 15              | -               | ± 1               | μА   |

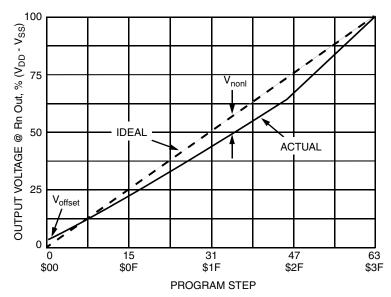

| V <sub>nonl</sub> | Nonlinearity Voltage (Rn Out)                         | See Figure 3                               | 5<br>10<br>15   | -<br>-<br>-     | 100<br>200<br>300 | mV   |

MC144110 Technical Data, Rev. 2

#### **Table 2. Electrical Characteristics (continued)**

(Voltages referenced to  $V_{SS}$ ,  $T_A = 0$  to  $85^{\circ}$ C unless otherwise indicated)

| Symbol              | Parameter                           | Test Conditions                                          | $V_{DD}$      | Min            | Max               | Unit |

|---------------------|-------------------------------------|----------------------------------------------------------|---------------|----------------|-------------------|------|

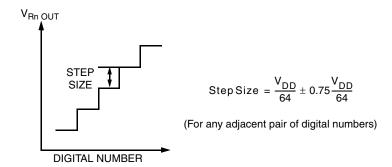

| V <sub>step</sub>   | Step Size (Rn Out)                  | See Figure 4                                             | 5<br>10<br>15 | 19<br>39<br>58 | 137<br>274<br>411 | mV   |

| V <sub>offset</sub> | Offset Voltage from V <sub>SS</sub> | D <sub>in</sub> = \$00, See Figure 3                     | -             | -              | 1                 | LSB  |

| ΙE                  | Emitter Leakage Current             | V <sub>Rn Out</sub> = 0 V                                | 15            | -              | 10                | μΑ   |

| h <sub>FE</sub>     | DC Current Gain                     | I <sub>E</sub> = 0.1 to 10.0 mA<br>T <sub>A</sub> = 25°C | -             | 40             | -                 | -    |

| V <sub>BE</sub>     | Base-to-Emitter Voltage Drop        | I <sub>E</sub> = 1.0 mA                                  | -             | 0.4            | 0.7               | V    |

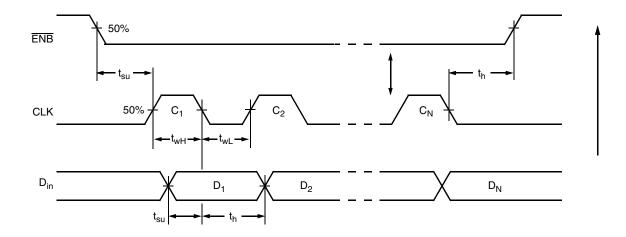

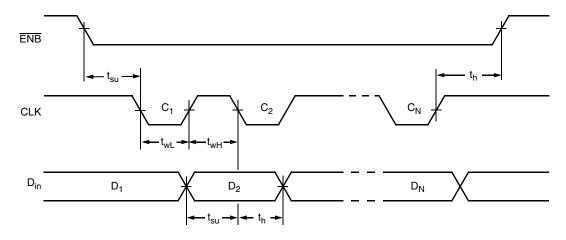

## 3 Switching Characteristics

#### **Table 3. Switching Characteristics**

(Voltages referenced to  $V_{SS}$ ,  $T_A = 0$  to  $85^{\circ}$ C,  $C_L = 50$  pF, Input  $t_r = t_f = 20$  ns unless otherwise indicated)

| Symbol                          | Parameter                                            | V <sub>DD</sub> | Min  | Max | Unit |

|---------------------------------|------------------------------------------------------|-----------------|------|-----|------|

| t <sub>wH</sub>                 | Positive Pulse Width, CLK (Figures 5 and 6)          | 5               | 2    | -   | μS   |

|                                 |                                                      | 10              | 1.5  | -   |      |

|                                 |                                                      | 15              | 1    | -   |      |

| t <sub>wL</sub>                 | Negative Pulse Width, CLK (Figure 5 and 6)           | 5               | 5    | -   | μS   |

|                                 |                                                      | 10              | 3.5  | -   |      |

|                                 |                                                      | 15              | 2    | -   |      |

| t <sub>su</sub>                 | Setup Time, ENB to CLK (Figures 5 and 6)             | 5               | 5    | -   | μS   |

|                                 |                                                      | 10              | 3.5  | -   |      |

|                                 |                                                      | 15              | 2    | -   |      |

| t <sub>su</sub>                 | Setup Time, D <sub>in</sub> to CLK (Figures 5 and 6) | 5               | 1000 | -   | ns   |

|                                 |                                                      | 10              | 750  | -   |      |

|                                 |                                                      | 15              | 500  | -   |      |

| t <sub>h</sub>                  | Hold Time, CLK to ENB (Figures 5 and 6)              | 5               | 5    | -   | μS   |

|                                 |                                                      | 10              | 3.5  | -   |      |

|                                 |                                                      | 15              | 2    | -   |      |

| t <sub>h</sub>                  | Hold Time, CLK to D <sub>in</sub> (Figures 5 and 6)  | 5               | 5    | -   | μS   |

|                                 |                                                      | 10              | 3.5  | -   |      |

|                                 |                                                      | 15              | 2    | -   |      |

| t <sub>r</sub> , t <sub>f</sub> | Input Rise and Fall Times                            | 5 - 15          | -    | 2   | μS   |

| C <sub>in</sub>                 | Input Capacitance                                    | 5 - 15          | -    | 7.5 | pF   |

**LINEARITY ERROR (integral linearity)**. A measure of how straight a device's transfer function is, it indicates the worst-case deviation of linearity of the actual transfer function from the best-fit straight line. It is normally specified in parts of an LSB.

Figure 3. D/A Transfer Function

Figure 4. Definition of Step Size

Figure 5. Serial Input, Positive Clock

Figure 6. Serial Input, Negative Clock

Table 4. Number of Channels vs Clocks Required

| Number of Channels<br>Required | Number of Clock Cycles | Outputs Used on MC144110                 | Outputs Used on MC144111   |

|--------------------------------|------------------------|------------------------------------------|----------------------------|

| 1                              | 6                      | Q1/R1                                    | Q1/R1                      |

| 2                              | 12                     | Q1/R1, Q2/R2                             | Q1/R1, Q2/R2               |

| 3                              | 18                     | Q1/R1, Q2/R2, Q3/R3                      | Q1/R1, Q2/R2, Q3/R3        |

| 4                              | 24                     | Q1/R1, Q2/R2, Q3/R3, Q4/R4               | Q1/R1, Q2/R2, Q3/R3, Q4/R4 |

| 5                              | 30                     | Q1/R1, Q2/R2, Q3/R3, Q4/R4, Q5/R5        | Not Applicable             |

| 6                              | 36                     | Q1/R1, Q2/R2, Q3/R3, Q4/R4, Q5/R5, Q6/R6 | Not Applicable             |

**Pin Descriptions**

## 4 Pin Descriptions

#### 4.1 INPUTS

#### Din

#### **Data Input**

Six-bit words are entered serially, MSB first, into digital data input, D<sub>in</sub>. Six words are loaded into the MC144110 during each D/A cycle; four words are loaded into the MC144111.

The last 6-bit word shifted in determines the output level of pins Q1 Out and R1 Out. The next-to-last 6-bit word affects pins Q2 Out and R2 Out, etc.

#### **ENB**

#### **Negative Logic Enable**

The  $\overline{\text{ENB}}$  pin must be low (active) during the serial load. On the low-to-high transition of  $\overline{\text{ENB}}$ , data contained in the shift register is loaded into the latch.

#### **CLK**

#### **Shift Register Clock**

Data is shifted into the register on the high-to-low transition of CLK. CLK is fed into the D-input of a transparent latch, which is used for inhibiting the clocking of the shift register when ENB is high.

The number of clock cycles required for the MC144110 is usually 36. The MC144111 usually uses 24 cycles. See Table 4 for additional information.

#### 4.2 OUTPUTS

### **D**out

## **Data Output**

The digital data output is primarily used for cascading the DACs and may be fed into  $D_{in}$  of the next stage.

## R1 Out through Rn Out Resistor Network Outputs

These are the R-2R resistor network outputs. These outputs may be fed to high-impedance input FET op amps to bypass the on-chip bipolar transistors. The R value of the resistor network ranges from 7 to 15 k $\Omega$ .

## Q1 Out through Qn Out NPN Transistor Outputs

Buffered DAC outputs utilize an emitter-follower configuration for current-gain, thereby allowing interface to low-impedance circuits.

#### 4.3 SUPPLY PINS

## $V_{SS}$

## **Negative Supply Voltage**

This pin is usually ground.

## $V_{DD}$

## **Positive Supply Voltage**

The voltage applied to this pin is used to scale the analog output swing from 4.5 to 15 V p-p.

## 5 Packaging

#### NOTES:

- POSITIONAL TOLERANCE OF LEADS (D).

SHALL BE WITHIN 0.25 (0.010) AT MAXIMUM MATERIAL CONDITION, IN RELATION TO SEATING PLANE AND EACH OTHER.

- DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL.

- 3. DIMENSION B DOES NOT INCLUDE MOLD FLASH.

- 4. CONTROLLING DIMENSION: INCH.

|     | INCHES    |                  | MILLIM | IETERS |  |

|-----|-----------|------------------|--------|--------|--|

| DIM | MIN       | MAX              | MIN    | MAX    |  |

| Α   | 0.875     | 0.915            | 22.22  | 23.24  |  |

| В   | 0.240     | 0.260            | 6.10   | 6.60   |  |

| C   | 0.140     | 0.180            | 3.56   | 4.57   |  |

| D   | 0.014     | 0.022            | 0.36   | 0.56   |  |

| F   | 0.050     | 0.070            | 1.27   | 1.78   |  |

| G   | 0.100     | BSC 2.54 BSC     |        | BSC    |  |

| Н   | 0.040     | 0.060            | 1.02   | 1.52   |  |

| ſ   | 0.008     | 0.012            | 0.20   | 0.30   |  |

| K   | 0.115     | 5 0.135 2.92 3.4 |        | 3.43   |  |

| L   | 0.300 BSC |                  | 7.62   | BSC    |  |

| M   | 0°        | 15°              | 0°     | 15°    |  |

| И   | 0.020     | 0.040            | 0.51   | 1.02   |  |

Figure 7. Outline Dimensions for P SUFFIX, PLASTIC DIP (CASE 707-02, Issue C)

Figure 8. Outline Dimensions for DW SUFFIX, SOG (CASE 751D-06, Issue H)

MC144110 Technical Data, Rev. 2

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1994.

2. CONTROLLING DIMENSION: INCH.

3. DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL.

4. DIMENSION B DOES NOT INCLUDE MOLD FLASH.

5. ROUNDED CORNERS OPTIONAL.

6. 646-06 OBSOLETE, NEW STANDARD 646-07.

|     | INCHES    |       |  |

|-----|-----------|-------|--|

| DIM | MIN       | MAX   |  |

| Α   | 0.715     | 0.770 |  |

| В   | 0.240     | 0.260 |  |

| C   | 0.145     | 0.185 |  |

| D   | 0.015     | 0.021 |  |

| F   | 0.040     | 0.070 |  |

| G   | 0.100 BSC |       |  |

| Н   | 0.052     | 0.095 |  |

| 7   | 0.008     | 0.015 |  |

| K   | 0.115     | 0.135 |  |

| L   | 0.290     | 0.310 |  |

| M   |           | 10°   |  |

| N   | 0.015     | 0.040 |  |

Figure 9. Outline Dimensions for P SUFFIX, PLASTIC DIP (CASE 646-07, Issue P)

Figure 10. Outline Dimensions for DW SUFFIX, SOG (CASE 751G-04, Issue D)

#### How to Reach Us:

#### Home Page:

www.freescale.com

#### E-mail:

support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

RoHS-compliant and/or Pb- free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb- free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale.s Environmental Products program, go to http://www.freescale.com/epp.

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale ™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2005. All rights reserved.